# ECE 413: Intro to VLSI

# Assignment 5: Two-Bit Full Adder Design

**Roderick Renwick**

November 20, 2019 Fall 2019

Honor Code:

I have neither given nor received unauthorized assistance on this graded report.

X\_\_\_\_\_Roderick\_Renwick\_\_\_\_\_

# **Table of Contents**

| Table of Contents           | 2  |

|-----------------------------|----|

| Introduction                | 3  |

| Design: One-Bit-Full-Adder  | 4  |

| Design: NAND Gate           | 6  |

| Design: XOR Gate            | 7  |

| Design: INV Gate            | 8  |

| Design: Two-Bit-Full-Adder  | 9  |

| Implementation & Simulation | 10 |

| L-Edit Results              | 15 |

| DRC Verification            | 17 |

| Conclusion                  | 18 |

|                             |    |

#### Introduction

The following laboratory procedure lays out the construction of a two-bit full adder and its transistor layout composed of CMOS inverters that are grouped into NAND and XOR logic gates.

#### Design: One-Bit-Full-Adder

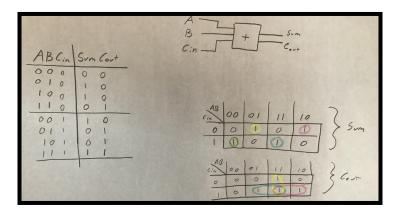

To realize a two-bit-full-adder, the one-bit-full-adder must be designed first. The following figures provide the truth table, optimized kmap functions, and logic-gate layout for a one-bit-full-adder:

**One-Bit-Full-Adder Truth Table & K-Maps**

| Sum = ABC + ABC + ABC + ABC                              |

|----------------------------------------------------------|

| = C(A'B'+AB) + C'(A'B+AB')                               |

| $= C\left(\overline{A'B + AB'}\right) + C'(A \oplus B)$  |

| $= C\left(\overline{A \oplus B}\right) + C'(A \oplus B)$ |

| $= A \oplus B \oplus C$                                  |

| Cout = AB + AC + BC                                      |

| = AB + C(A+B)                                            |

| $= AB + C(A \oplus B)$                                   |

| $=\overline{(\overline{AB})(\overline{C(ABB)})}$         |

**One-Bit-Full-Adder Boolean Algebra Optimization**

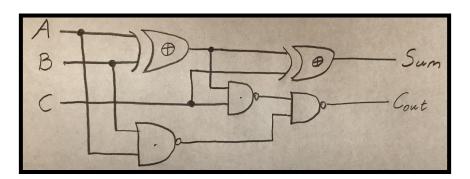

**One-Bit-Full-Adder Logic-Gate Design**

Candidate Layout for One-Bit Adder Desgin

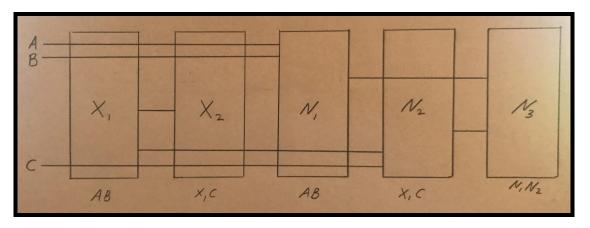

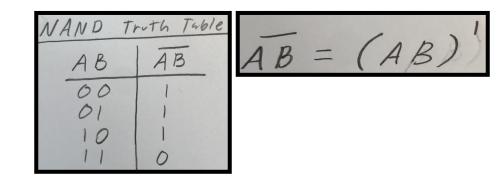

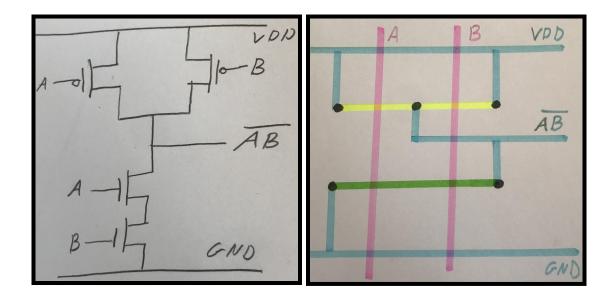

### **Design: NAND Gate**

The truth table, optimized functions, circuit design, and transistor-level layout for a two-input NAND gate are as follows:

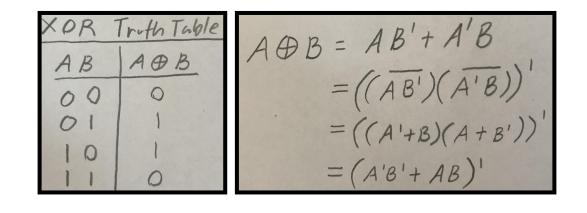

### **Design: XOR Gate**

The truth table, optimized functions, circuit design, and transistor-level layout for a two-input XOR gate are as follows:

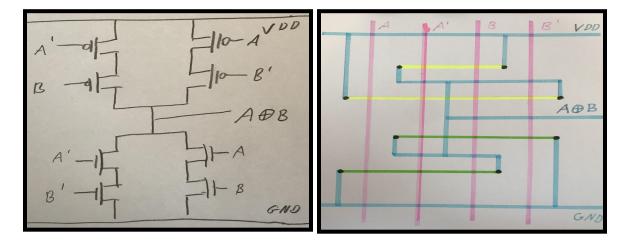

# **Design: INV Gate**

The truth table, optimized functions, circuit design, and transistor-level layout for an Inverter gate is as follows (note that this is done for both inputs A, and B):

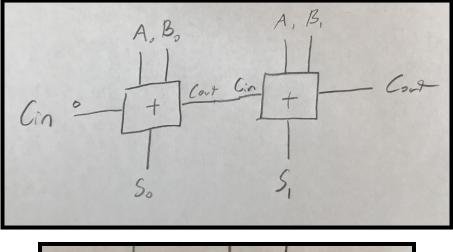

#### Design: Two-Bit-Full-Adder

Following the design and layout of transistors to construct a NAND gate, Inverter Gate, and an XOR gate, required to realize a one-bit-full-adder, a two-bit-full-adder may then be implemented by connecting two one-bit-full-adders together. This is done by taking the carr-out of the first adder and feeding it into the carry-in of the second adder, while at the same time feeding the compliments of the A and B inputs into the second adder. The design and truth table for the two-bit-full-adder are as follows:

| A. A. | B. B. | Cin | 505, Cort |

|-------|-------|-----|-----------|

| 00    | 00    | 0   | 000       |

| 10    | 00    | 0   | 100       |

| 01    | 00    | 0   | 010       |

| 10    | 10    | 0   | 010       |

| 01    | 0 1   | 0   | 001       |

| 01    | 00    | 1   | 110       |

| 10    | 10    | 11  | 110       |

| )     | 1 1 1 | 11  | 11-1      |

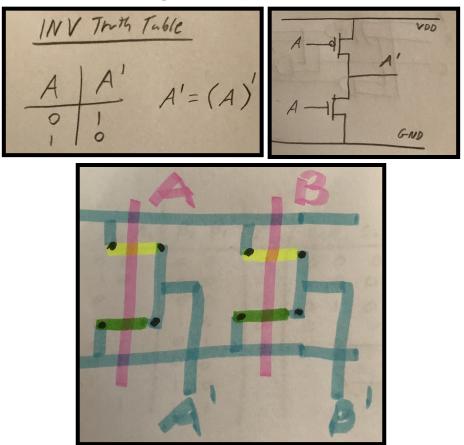

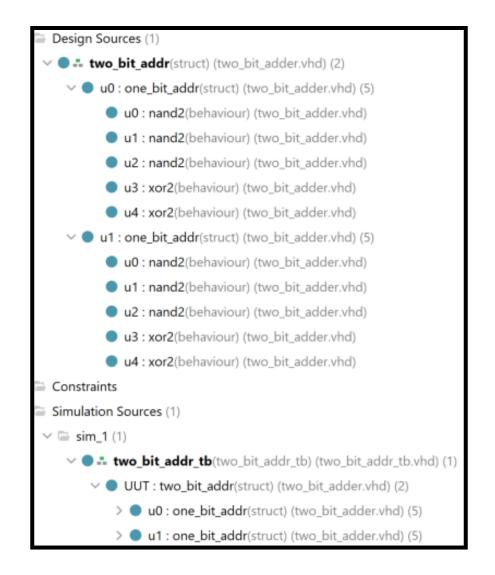

#### **Implementation & Simulation**

The following figures show the logical simulation of the two-bit-full-adder through valvalo software to verify and validate the design implementation:

```

ibrary IEEE;

use IEEE.STD LOGIC 1164.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity nand2 is

-- NAND GATE ENTITY DECLARATION

port (

i0, i1 : in std logic;

o : out std logic

);

end nand2;

architecture behaviour of nand2 is -- NAND_GATE ARCHITECTURE DECLARATION

begin

end behaviour;

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity xor2 is

-- XOR GATE ENTITY DECLARATION

port (

i0, i1 : in std_logic;

o : out std_logic

);

end xor2;

architecture behaviour of xor2 is -- XOR GATE ARCHITECTURE DECLARATION

begin

o <= not ( ( not ( i0 and i1 ) ) and i0 ) ) and ( not ( i0 and i1 ) ) and i1 ) );

end behaviour;

```

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity one bit addr is

-- 2-bit adder ENTITY DECLARATION

Port (

X in : in STD LOGIC;

Y in : in STD LOGIC;

C in : in STD LOGIC;

S out : out STD LOGIC;

C_out : out STD_LOGIC

);

end one bit addr;

architecture struct of one bit addr is -- 2-bit adder ARCHITECTURE DECLARATION

component nand2

-- NAND GATE Component Declaration

port (

i0, i1: in std_logic;

o : out std_logic

);

end component;

component xor2

-- XOR GATE component declaration

port (

i0, i1 : in std_logic;

o : out std logic

);

end component;

```

```

-- Internal Signals Declarations

signal xor0 : std_logic;

signal nand0 : std_logic;

signal nand1 : std_logic;

```

begin

```

-- Component Instantiations Statements

u0 : nand2 port map ( i0 => X_in, i1 => Y_in, o => nand0 );

u1 : nand2 port map ( i0 => xor0, i1 => C_in, o => nand1 );

u2 : nand2 port map ( i0 => nand0, i1 =>nand1, o => C_out );

u3 : xor2 port map ( i0 => X_in, i1 => Y_in, o => xor0 );

u4 : xor2 port map ( i0 => xor0, i1 => C_in, o => S_out );

end struct;

```

```

library IEEE;

ise IEEE.STD_LOGIC_1164.ALL;

library UNISIM;

use UNISIM.VComponents.all;

-- 2-bit adder ENTITY DECLARATION

entity two_bit_addr is

Port (

X0_in : in STD_LOGIC;

Y0_in : in STD_LOGIC;

X1 in : in STD LOGIC;

Y1_in : in STD_LOGIC;

C_in : in STD_LOGIC;

C_out : out STD_LOGIC;

S0_out : out STD_LOGIC;

S1_out : out STD_LOGIC

);

end two_bit_addr;

architecture struct of two_bit_addr is-- 2-bit adder ARCHITECTURE DECLARATION

component one_bit_addr

-- NAND_GATE Component Declaration

port (

X_in, Y_in, C_in: in std_logic;

C_out, S_out : out std_logic

);

end component;

-- Internal Signals Declarations

signal c_out_signal : std_logic;

pegin

-- Component Instantiations Statements

u0 : one_bit_addr port map (X_in => X0_in, Y_in => Y0_in, C_in => C_in, C_out => c_out_signal, S_out => S0_out );

u1 : one_bit_addr port map (X_in => X1_in, Y_in => Y1_in, C_in => c_out_signal, C_out => C_out, S_out => S1_out );

struct

```

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity two bit addr tb is

end two bit addr tb;

architecture two bit addr tb of two bit addr tb is

component two bit addr is

Port (

X0 in : in STD LOGIC;

Y0 in : in STD LOGIC;

X1 in : in STD LOGIC;

Y1 in : in STD LOGIC;

C in : in STD LOGIC;

C out : out STD LOGIC;

S0 out : out STD LOGIC;

S1 out : out STD LOGIC

);

end component;

signal X0 in : std logic := '0';

signal X1_in : std_logic := '0';

signal Y0 in : std logic := '0';

signal Y1 in : std logic := '0';

signal C in : std logic := '0';

signal C out : std logic;

signal S0 out : std logic;

signal S1 out : std logic;

```

#### begin

| Name              | Value | 0 ns | 100 | ns | 200 ns |    | 300 n | s |   | 00 ns |    | 500 n: | 5 | 60 | 0 ns | 700 ns | 800 ns |    | 900 ns |  |

|-------------------|-------|------|-----|----|--------|----|-------|---|---|-------|----|--------|---|----|------|--------|--------|----|--------|--|

| 🔓 X0_in           |       |      |     |    | Ш      | ШП | Ш     |   | Ш | Ш     | ШП |        | Ш |    |      |        |        | ШП |        |  |

| 😼 X1_in           | 0     |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

| 🔓 Y0_in           | 0     |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

| 🔓 Y1_in           | 1     |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

| <mark>℃_in</mark> | 0     |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

| 🔓 C_out           | 0     |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

| 😼 S0_ou           | 1     |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

| 🔓 S1_ou           | 1     |      |     |    |        |    |       |   |   |       |    |        |   | Т  |      |        |        |    |        |  |

|                   |       |      |     |    |        |    |       |   |   |       |    |        |   |    |      |        |        |    |        |  |

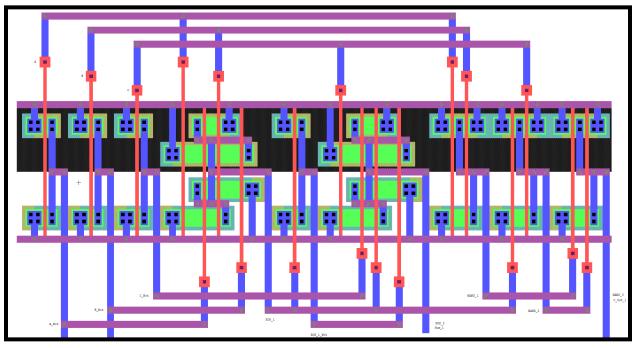

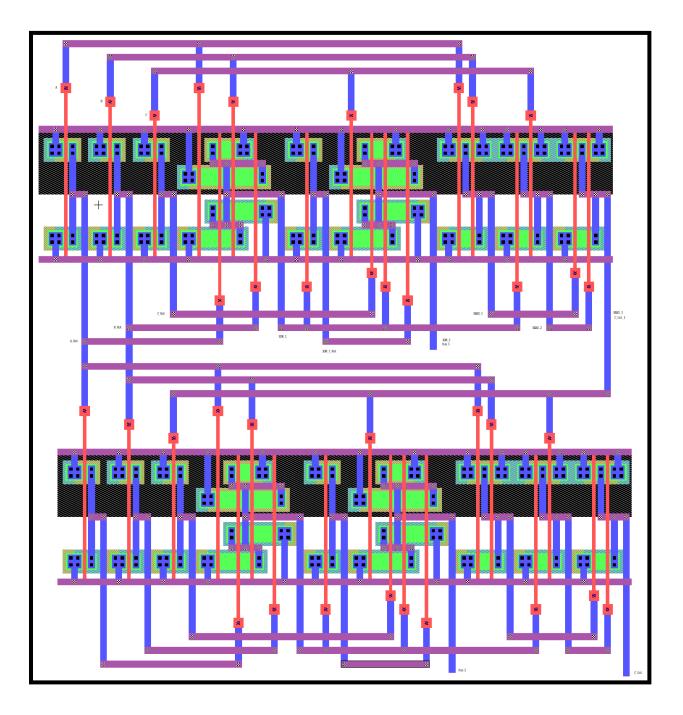

# L-Edit Results

Here is the resulting L-Edit layout of a one-bit-full-adder:

Here is the resulting L-Edit layout of a two-bit-full-adder, after connecting two one-bit-full-adders together as laid out in the design steps above:

### **DRC Verification**

Here are the resulting DRC check verification messages and file:

| Cell0.txt - Notepad            |                                                                                                   |

|--------------------------------|---------------------------------------------------------------------------------------------------|

| File Edit Format View Help     |                                                                                                   |

| DRC Errors in cell Cell0 of fi | le C:\Users\RoderickLRenwick\Documents\03_mySchoolStuff\05_UMD_Fall_2019\ECE_413_VLSI\HW_5\adder. |

| 0 errors.                      |                                                                                                   |

| DRC Merge/Gen Layers Elapsed T | ime: 0.000000 seconds.                                                                            |

| DRC Test Elapsed Time: 0.00000 | 0 seconds.                                                                                        |

| DRC Elapsed Time: 0 seconds.   |                                                                                                   |

|                                | L-Edit ×<br>No DRC errors found.                                                                  |

|                                | ОК                                                                                                |

#### Conclusion

The homework was successfully verified and validated from both the software implementation in Valvado, and the hardware layout design in L-Edit. Overall, I learned a lot from this lab. It really challenged me to think carefully and plan ahead for the layout from start to finish.