# ECE 413: Intro to VLSI

# **Assignment 1: Transistor Layout Introduction**

#### Roderick Renwick

October 03, 2019 Fall 2019

| Honor Code:    |                                                                   |  |

|----------------|-------------------------------------------------------------------|--|

| I have neither | given nor received unauthorized assistance on this graded report. |  |

| $\mathbf{v}$   | Dodowialz Donyvialz                                               |  |

# **Table of Contents**

| Table of Contents       | 2 |

|-------------------------|---|

| NMOS                    | 3 |

| PMOS                    | 4 |

| CMOS Inverter           | 5 |

| Cascaded CMOS Inverters | 7 |

| DRC Files               | 8 |

| Conclusion              | 9 |

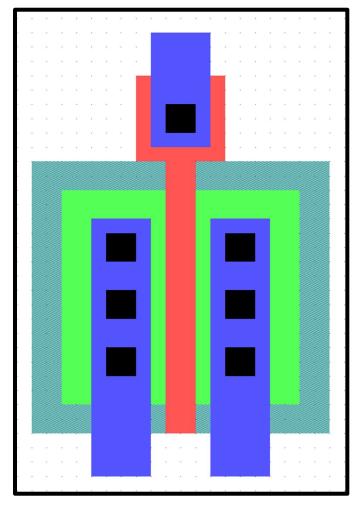

## **NMOS**

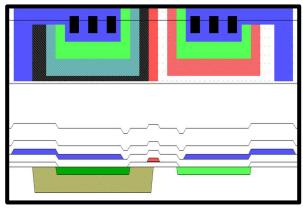

The following figure shows an NMOS transistor layout.

Figure-1: NMOS

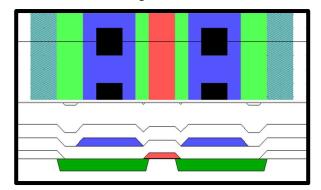

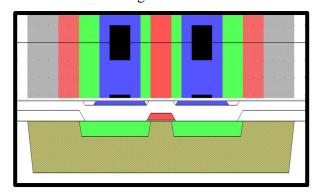

Here are the resulting cross section views for the NMOS transistor shown above.

Figure-2: Horizontal Cross-Section of NMOS

Figure-3: Vertical Cross-Section of NMOS

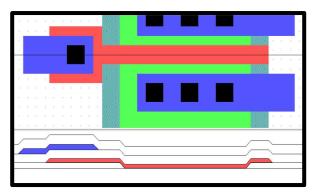

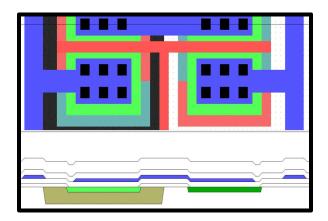

## **PMOS**

The following figure shows a PMOS transistor layout (noting the N-Well layer on top of the substrate).

Figure-4: PMOS

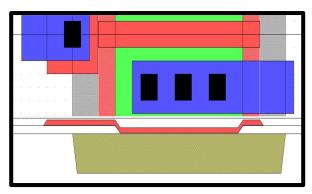

Here are the resulting cross section views for the PMOS transistor shown above.

Figure-5: Horizontal Cross-Section of PMOS

Figure-6: Vertical Cross-Section of PMOS

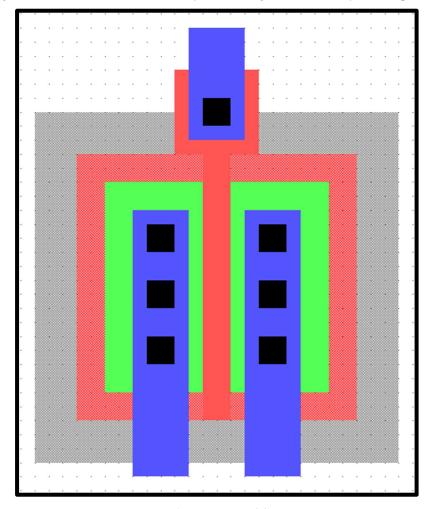

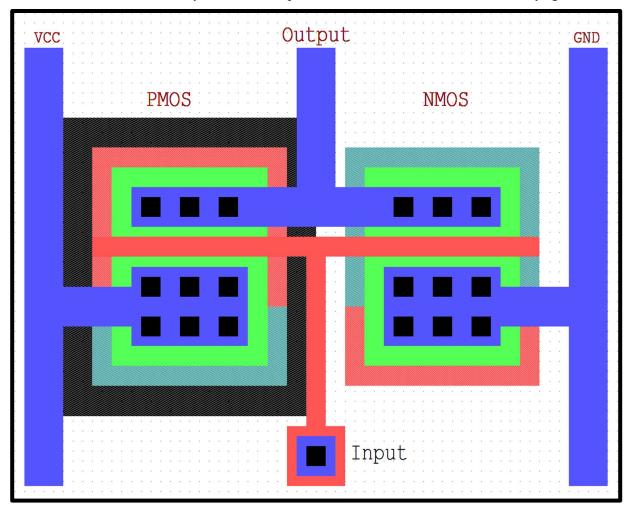

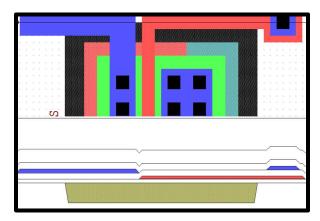

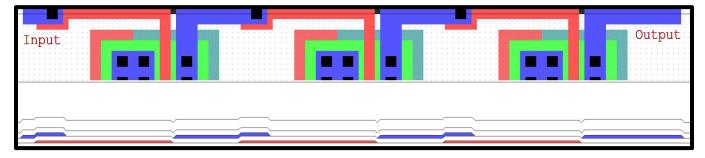

## **CMOS Inverter**

The following figure shows a CMOS Inverter transistor layout made from the NMOS and PMOS. Note that the PMOS transistor is always connected to power, while the NMOS transistor is always grounded.

Figure-7: CMOS Inverter

Here are the resulting cross section views for the CMOS Inverter transistor shown on the previous page.

Figure-8: Horizontal Cross-Section of CMOS

Figure-9: Horizontal Cross-Section of CMOS

Figure-10: Metal1 Cross-Section of CMOS

Figure-11: I/O Cross-Section of CMOS

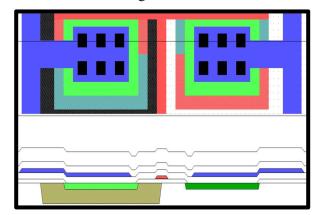

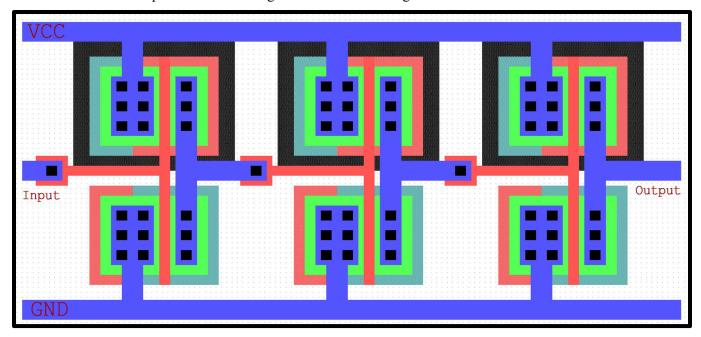

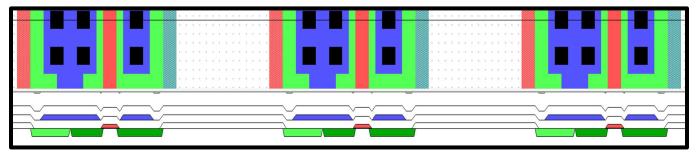

#### **Cascaded CMOS Inverters**

The following figure shows three cascaded CMOS Inverter transistors. Note that the outputs of the prior CMOS drive the inputs of the following CMOS from left to right.

Figure-12: Cascaded CMOS Inverters

Here are the resulting cross section views for the cascaded CMOS Inverters as shown above.

Figure-13: Horizontal Cross-Section of CMOS Inverter

Figure-14: Horizontal Cross-Section of CMOS Inverter

#### **DRC Files**

The DRC files for the simulations are as follows:

#### ###Procedures

```

MNMOS_DRC.txt-Notepad

File Edit Format View Help

DRC Errors in cell Cell0 of file C:\Users\RoderickLRenwick\Documents\03_mySchoolStuff\05_UMD_Fall_2019\ECE_413_VLSI\NMOS_Trial1.

0 errors.

DRC Merge/Gen Layers Elapsed Time: 0.000000 seconds.

DRC Test Elapsed Time: 0.000000 seconds.

DRC Elapsed Time: 0 seconds.

```

Figure-15: NMOS DRC File (total errors = 0)

```

PMOS_DRC.txt-Notepad

File Edit Format View Help

DRC Errors in cell Cell0 of file C:\Users\RoderickLRenwick\Documents\03_mySchoolStuff\05_UMD_Fall_2019\ECE_413_VLSI\assignments\finished\PMOS_TDB.

0 errors.

DRC Merge/Gen Layers Elapsed Time: 0.000000 seconds.

DRC Test Elapsed Time: 0.000000 seconds.

DRC Elapsed Time: 0 seconds.

```

Figure-16: PMOS DRC File (total errors = 0)

```

GMOS_INV_DRC.txt-Notepad

File Edit Format View Help

DRC Errors in cell Cell0 of file C:\Users\RoderickLRenwick\Documents\03_mySchoolStuff\05_UMD_Fall_2019\ECE_413_VLSI\CMOS_Trial_0.

0 errors.

DRC Merge/Gen Layers Elapsed Time: 0.000000 seconds.

DRC Test Elapsed Time: 0.000000 seconds.

DRC Elapsed Time: 0 seconds.

```

Figure-17: CMOS Inverter DRC File (total errors =  $\theta$ )

```

□ CASCADED_CMOS_INV_DRC.txt - Notepad

□ CASCADED_CMOS_INV_DRC.txt - Notepad

□ X

File Edit Format View Help

DRC Errors in cell Cell0 of file C:\Users\RoderickLRenwick\Documents\03_mySchoolStuff\05_UMD_Fall_2019\ECE_413_VLSI\assignments\finished\CASCADED_CMOS_INV_TDB.

0 errors.

DRC Merge/Gen Layers Elapsed Time: 0.000000 seconds.

DRC Test Elapsed Time: 0.000000 seconds.

DRC Elapsed Time: 0 seconds.

```

Figure-18: Cascaded CMOS Inverters DRC File (total errors = 0)

## Conclusion

Overall I think that this simulation is a fantastic way to learn about transistors and makes the topic very fun to learn about. I am enjoying the hands-on approach to constructing and design these transistors and I believe that it helps solidify the concepts immensely.